在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体:

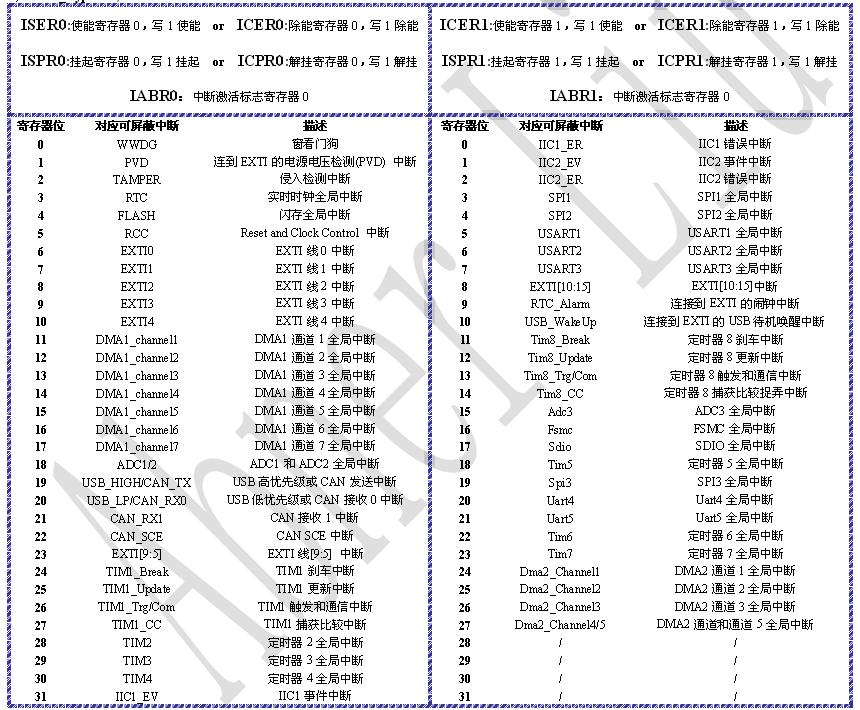

typedef struct { vu32 ISER[2]; //2个32位中断使能寄存器分别对应到60个可屏蔽中断 u32 RESERVED0[30]; vu32 ICER[2]; //2个32位中断除能寄存器分别对应到60个可屏蔽中断 u32 RSERVED1[30]; vu32 ISPR[2]; //2个32位中断挂起寄存器分别对应到60个可屏蔽中断,可挂起正在执行的中断 u32 RESERVED2[30]; vu32 ICPR[2]; //2个32位中断解挂寄存器分别对应到60个可屏蔽中断,可解除被挂起的中断 u32 RESERVED3[30]; vu32 IABR[2]; //2个32位中断激活标志寄存器,可读取该寄存器判断当前执行的中断是哪个,中断执行完硬件清零,只读 u32 RESERVED4[62]; vu32 IPR[15]; //15个32位中断优先级分组寄存器,每个中断分配8个bit,对应到4*15=60个中断 } NVIC_TypeDef;

IPR[15]

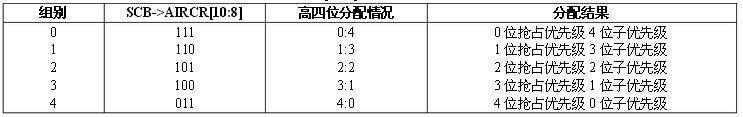

15个32位中断优先级分组寄存器,每个中断分配8个bit,对应到4*15=60个中断。但是并不是8个bit都被使用了,而是仅仅只用到了高四位,这样就可以得到5组16级的中断优先级。高位的4个bit又分为抢占优先级和子优先级,抢占优先级在前,子优先级在后。两种类型优先级占用的位数又可以通过SCB->AIRCR寄存器的bit[10:8]来配置。

数字越小优先级越高,高优先级的中断可以中断低优先级的中断,但是抢占优先级相同时子优先级高的无法中断子优先级低的中断。

结合实例说明一下:假定设置中断优先级组为2,然后设置中断28(Tim2中断)的抢占优先级为3,响应优先级为2。中断6(外部中断0)的抢占优先级为4,响应优先级为0。中断7(外部中断1)的抢占优先级为3,响应优先级为0。那么这3个中断的优先级顺序为:中断7>中断28>中断6。

上面例子中的中断28和中断7都可以打断中断6的中断。而中断7和中断28却不可以相互打断!